- 您现在的位置:买卖IC网 > Sheet目录1204 > CSIX-LEV1-O4-N1 (Lattice Semiconductor Corporation)INTERFACE IP CSIX LEVEL 1 ORCA 4

�� �

�

Lattice� Semiconductor�

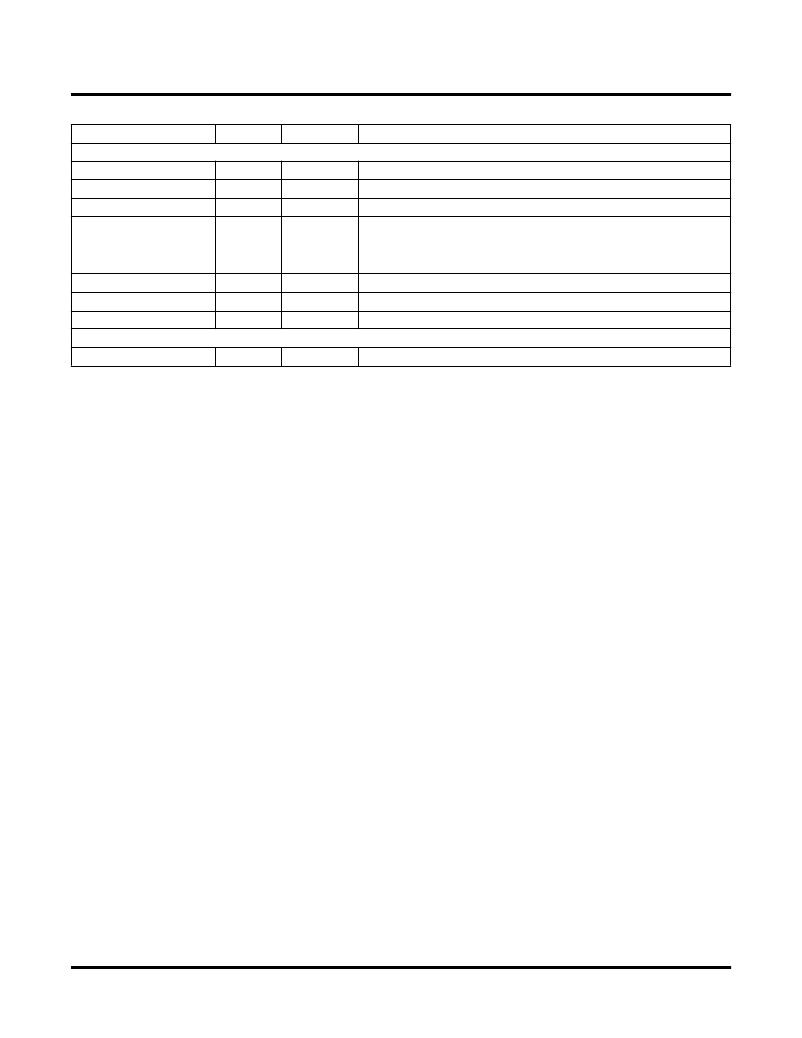

�Table� 2.� Signal� De?nitions� of� CSIX� Level� 1� Core� (Continued)�

�CSIX� Level� 1� IP� Core� User’s� Guide�

�Signal� Name� 1�

�Direction�

�Width� (Bits)�

�Description�

�Register� Interface� (These� signals� are� buried� inside� the� FPGA� –� do� not� replicate)�

�us_clk�

�us_addr[17:0]�

�us_wdata[7:0]�

�us_rdata[31:0]�

�Input�

�Input�

�Input�

�Output�

�1�

�18�

�8�

�32�

�Clock� (50MHz)�

�Address� bits�

�Input� Data� Bus�

�Output� Data� Bus,� HiZ� except� during� read� cycle� and� us_addr� matches�

�one� of� the� implemented� register� addresses.� Note� the� core� only� imple-�

�ments� 8-bit� registers.� For� read� accesses,� byte� wide� register� outputs� are�

�copied� to� all� four� bytes� of� the� sysbus� interface.�

�us_ready�

�us_wr�

�us_ack�

�Input�

�Input�

�Output�

�1�

�1�

�1�

�Bus� Cycle� Enable� (Active� Low)�

�Write� High/� Read� Low�

�Bus� Cycle� Acknowledge�

�Global� (These� signals� are� buried� inside� the� FPGA� –� do� not� replicate)�

�rst_n�

�input�

�1�

�Active� Low� Global� Reset�

�1.� N� denotes� instantiated� channel� number� (0,� 1,� 2,� 3).�

�Functional� Description�

�Inbound� Path�

�The� inbound� path� monitors� the� inbound� CSIX� port� and� writes� valid� Cframes� into� control� and� data� FIFOs.� User�

�applications� may� access� the� stored� Cframes� via� the� two� inbound� Generic� FIFO� Bridge� interfaces.� Major� functions�

�of� inbound� path� include:� distinguishing� control� and� data� Cframes,� directing� Cframe� writes� to� the� appropriate� FIFO,�

�?ltering� idle� Cframes� from� the� FIFOs,� delineating� stored� Cframes� with� end-of-frame� ?ags,� checking� horizontal� and�

�vertical� parity,� and� facilitating� link-level� ?ow� control� and� backpressure.�

�The� inbound� core� utilizes� two� FIFOs;� one� for� data� Cframes,� the� other� for� control� Cframes.� Each� FIFO� has� program-�

�mable� high� and� low� watermarks.� When� the� low� watermark� is� asserted,� the� Generic� FIFO� Bridge� bus� is� signaled�

�that� a� frame� is� available� for� reading.� When� the� high� watermark� is� asserted,� a� “nearly-full”� signal� is� sent� to� the� IP�

�core’s� outbound� path� for� ?ow� control.� In� cases� where� a� FIFO� either� under?ows� or� over?ows,� a� corresponding� error�

�signal� is� sent� to� the� register� interface� for� storage.�

�An� inbound� write� controller� monitors� the� external� CSIX� port� and� writes� CSIX� data� frames� into� one� FIFO,� and� CSIX�

�control� frames� into� another� FIFO.�

�Horizontal� and� vertical� parity� are� checked� within� the� inbound� data� path.� The� checkers� can� be� enabled� via� control�

�signals� from� the� register� interface.� Any� detected� errors� cause� a� corresponding� error� signal� to� be� sent� to� the� register�

�interface� for� storage.�

�There� are� three� ?ow� control� mechanisms� associated� with� the� inbound� path.� The� ?rst� mechanism� passes� ready� bits�

�from� the� CSIX� interface� to� the� Local_Data_Ready� or� Local_Control_Ready� signals� alongside� the� Generic� FIFO�

�Bridge� interface.� These� signals� are� directly� connected� to� the� CSIX� ready� bits� at� the� second� stage� of� the� inbound�

�data� pipeline,� and� therefore� lag� the� external� CSIX� interface� by� two� clock� cycles.� The� local� ready� signals� give� user�

�applications� direct� access� to� the� CSIX� ready� status� without� having� to� wait� for� the� ready� status� to� percolate� through�

�the� FIFOs.�

�The� second� mechanism� is� associated� with� the� inbound� FIFOs.� If� either� FIFO� passes� its� high� watermark,� a� “nearly-�

�full”� signal� is� passed� to� the� outbound� datapath.� In� turn,� the� outbound� datapath� will� deassert� the� ready� bits� on� the�

�next� outbound� frame,� signaling� a� pause� to� the� transmitting� inbound� network� element.� This� mechanism� prevents� the�

�inbound� FIFOs� from� over?owing.�

�The� third� mechanism� is� associated� with� the� outbound� FIFOs.� If� either� outbound� FIFO� exceeds� its� high� watermark,�

�a� “nearly-full”� signal� is� sent� to� the� inbound� datapath.� In� turn,� the� inbound� datapath� deasserts� the� associated� local�

�5�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

CSIX-PI40-O4-N1

INTERFACE IP CSIX TO PI40 ORCA 4

CT0805S14BAUTOG

VARISTOR 14VRMS 0805 SMD AUTO

CT1206K17G

VARISTOR 17VRMS 1206 SMD

CTB-B-B-15

CIRCUIT BREAKER ROCKER 15A SP BK

CU3225K17AUTOG2

VARISTOR AUTO 17VRMS 3225 SMD

CU3225K250G2K1

VARISTOR STD 250VRMS 3225 SMD

CV10-RP-M-0

CONN JACK STR COAXIAL SMD

CVM50XM

MEMBER MOD PIC12C508/PIC12C509

相关代理商/技术参数

CSIX-PI40-O4-N1

功能描述:输入/输出控制器接口集成电路 CSIX to PI40 RoHS:否 制造商:Silicon Labs 产品: 输入/输出端数量: 工作电源电压: 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:QFN-64 封装:Tray

CSJ-100

制造商:GREENLEE TOOL CO 功能描述:Digital Open Jaw Clampmeter 制造商:Greenlee Textron Inc 功能描述:CLAMPMETER

CSJ-23

功能描述:EXTRACTION TOOL FOR SCS RoHS:否 类别:工具 >> 插入,抽取 系列:* 标准包装:1 系列:* 其它名称:0011-03-00080011-03-0008-E00110300080011030008-E11-03-0008-E1103000811030008-EQ4729393AT0980176A

CSJ32C1

制造商:未知厂家 制造商全称:未知厂家 功能描述:HC-49/US SMD Microprocessor Crystals

CSJ32C3

制造商:未知厂家 制造商全称:未知厂家 功能描述:HC-49/US SMD Microprocessor Crystals

CSJ32C5

制造商:未知厂家 制造商全称:未知厂家 功能描述:HC-49/US SMD Microprocessor Crystals

CSJ32E1

制造商:未知厂家 制造商全称:未知厂家 功能描述:HC-49/US SMD Microprocessor Crystals

CSJ32E3

制造商:未知厂家 制造商全称:未知厂家 功能描述:HC-49/US SMD Microprocessor Crystals